# OKI 電子デバイス

# MSM82C51A-2

Universal Synchronous Asynchronous Receiver Transmitter

#### ■ 概要

MSM82C51A-2は、マイクロコンピュータシステム用に開発された、シリアルデータ通信用USART (Universal Synchronous Receiver Transmitter)です。

MSM82C51A-2は、マイクロコンピュータシステム用の周辺デバイスとして、CPUよりパラレルデータを受け取りシリアルデータに変換して送出、また外部よりシリアルデータを受け取りパラレルデータに変換してCPUに送る等のデータ転送に適用できます。

MSM82C51A-2は、シリコンゲートCMOSテクノロジィを用い完全スタティック回路構成のため、全ての動作を停止する待機時には、電源電流 $100\mu$ A (MAX)と極めて低消費電力です。 機能はインテル社8251Aとコンパチブルです。

#### ■ 特長

- ●3~6Vの広い電源電圧範囲

- - 40~85 の広い温度保証範囲

- 64K Baudまでの同期通信

- 38.4K Baudまでの非同期通信

- ●2重バッファー構成による送受信動作

- ●エラー検出(パリティー、オーバーラン、フレーミング)

- ●インテル系バスコンパチブル

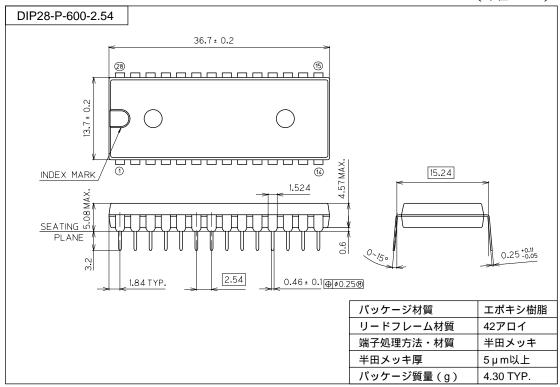

- ●28ピンプラスチックDIP(DIP28-P-600-2.54): (製品名:MSM82C51A-2RS)

- ●28ピンプラスチックQFJ(QFJ28-P-S450-1.27): (製品名: MSM82C51A-2JS)

- ●32ピンプラスチックSSOP(SSOP32-P-430-1.00-K):(製品名:MSM82C51A-2GS-K)

作成:1998年1月

前回作成:1996年8月

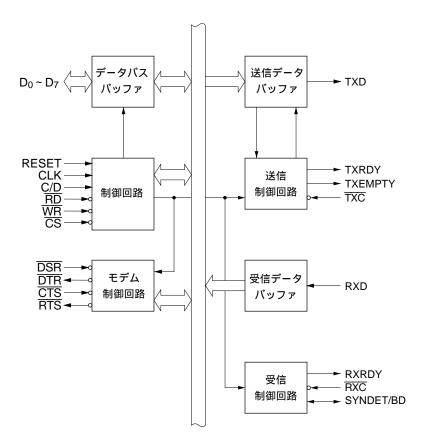

# ■ 回路構成

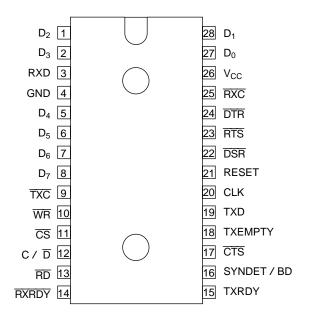

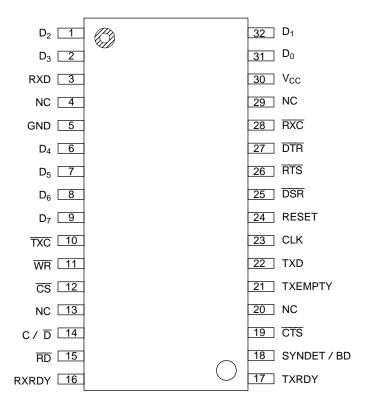

## ■ 端子接続(上面図)

#### 28ピンプラスチックDIP MSM82C51A-2RS

#### 32ピンプラスチックSSOP MSM82C51A-2GS-K

注記: NCは未使用端子。

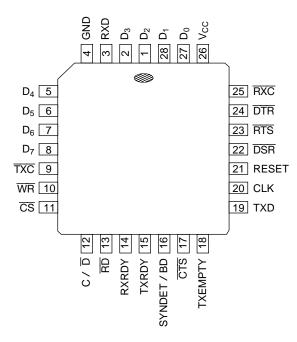

## 28ピンプラスチックQFJ MSM82C51A-2JS

# ■ 電気的特性

# ●絶対最大定格

| 項目   | 記号               | 条件              | 定村                 | 各値                    | 単位      |  |  |  |  |

|------|------------------|-----------------|--------------------|-----------------------|---------|--|--|--|--|

| 块口   | 記与               | 赤什              | MSM82C51A-2RS / JS | MSM82C51A-2GS         | 1 年11 1 |  |  |  |  |

| 電源電圧 | V <sub>CC</sub>  | ことの大甘油          | - 0.5              | ~ +7                  | V       |  |  |  |  |

| 入力電圧 | V <sub>IN</sub>  | GNDを基準<br>にした場合 | - 0.5 ~            | V <sub>CC</sub> + 0.5 | V       |  |  |  |  |

| 出力電圧 | V <sub>OUT</sub> | 1C 07C 36 1     | - 0.5 ~            | V <sub>CC</sub> + 0.5 | V       |  |  |  |  |

| 保存温度 | T <sub>STG</sub> |                 | - 55               | ~ 150                 |         |  |  |  |  |

| 許容損失 | P <sub>D</sub>   | Ta = 25         | 0.9                | 0.7                   | W       |  |  |  |  |

# ●動作範囲

| 項目       | 記号              | 範囲        | 単位 |

|----------|-----------------|-----------|----|

| 電源電圧     | Vcc             | 3 ~ 6     | V  |

| <br>動作温度 | T <sub>OP</sub> | - 40 ~ 85 |    |

# ●推奨動作条件

| 項目      | 記号              | Min.  | Тур. | Max.                  | 単位 |

|---------|-----------------|-------|------|-----------------------|----|

| 電源電圧    | V <sub>CC</sub> | 4.5   | 5    | 5.5                   | V  |

| 動作温度    | T <sub>OP</sub> | - 40  | + 25 | + 85                  |    |

| "L"入力電圧 | V <sub>IL</sub> | - 0.3 |      | + 0.8                 | ٧  |

|         | V <sub>IH</sub> | 2.2   |      | V <sub>CC</sub> + 0.3 | V  |

# ●直流特性

$$(V_{CC} = 4.5V \sim 5.5V, Ta = -40 \sim 85)$$

| 項目      | 記号               | 条件                                          | Min. | Тур. | Max. | 単位 |

|---------|------------------|---------------------------------------------|------|------|------|----|

| "L"出力電圧 | V <sub>OL</sub>  | I <sub>OL</sub> = 2.5mA                     |      |      | 0.45 | V  |

| "H"出力電圧 | V <sub>OH</sub>  | I <sub>OH</sub> = - 2.5mA                   | 3.7  |      | -    | V  |

| 入力リーク電流 | ILI              | 0 V <sub>IN</sub> V <sub>CC</sub>           | - 10 |      | 10   | μΑ |

| 出力リーク電流 | I <sub>LO</sub>  | 0 V <sub>OUT</sub> V <sub>CC</sub>          | - 10 | -    | 10   | μΑ |

| 動作時電源電流 | Icco             | T <sub>CYC</sub> = 250ns 非同期 x 64 送受信時      | -    | -    | 5    | mA |

| 待機時電源電流 | I <sub>CCS</sub> | 全入力端子はV <sub>CC</sub> 又はGND電位。<br>全出力端子は開放。 | -    | -    | 100  | μΑ |

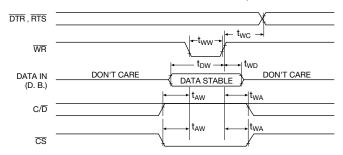

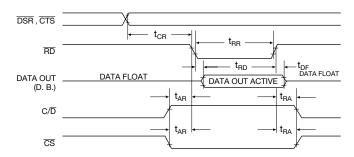

# ■ 交流特性 CPUバスインターフェース部

( V<sub>CC</sub> = 4.5V ~ 5.5V, Ta = -40 ~ 85 )

| 項目                     | 記号                | Min. | Max. | 単位              | 備考 |

|------------------------|-------------------|------|------|-----------------|----|

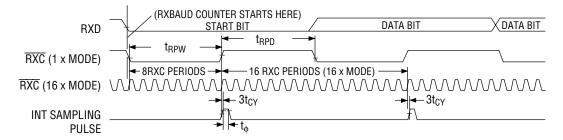

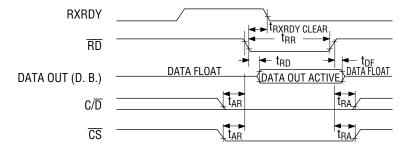

| RDの立下りに対するアドレスセットアップ時間 | t <sub>AR</sub>   | 20   | -    | ns              | 注2 |

| RDの立上りに対するアドレスホールド時間   | t <sub>RA</sub>   | 20   | -    | ns              | 注2 |

| RDパルス幅                 | t <sub>RR</sub>   | 130  | -    | ns              |    |

| RDの立下りからデーター確定時間       | t <sub>RD</sub>   | -    | 100  | ns              |    |

| RDの立上りからデータフロート時間      | t <sub>DF</sub>   | 10   | 75   | ns              |    |

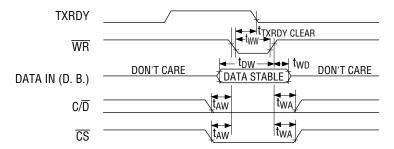

| WRの立下りに対するアドレスセットアップ時間 | t <sub>AW</sub>   | 20   | -    | ns              | 注2 |

| WRの立上りに対するアドレスホールド時間   | t <sub>WA</sub>   | 20   | -    | ns              | 注2 |

| WRのパルス幅                | t <sub>WW</sub>   | 100  | -    | ns              |    |

| WRの立上りに対すデータセットアップ時間   | t <sub>DW</sub>   | 100  | -    | ns              |    |

| WRの立上りに対するデータホールド時間    | t <sub>WD</sub>   | 0    | -    | ns              |    |

| WRパルス間隔(MODE設定時)       | t <sub>RVW</sub>  | 6    | -    | t <sub>CY</sub> |    |

| WRパルス間隔(非同期モードコマンド設定時) | t <sub>RVW</sub>  | 8    | -    | t <sub>CY</sub> |    |

| WRパルス間隔(同期モードコマンド設定時)  | t <sub>RVW</sub>  | 18   | -    | t <sub>CY</sub> |    |

| RDパルス間隔 (ステータスリード時)    | t <sub>RVR</sub>  | 6    | -    | t <sub>CY</sub> |    |

| RESETパルス幅              | t <sub>RESW</sub> | 6    | -    | t <sub>CY</sub> |    |

# シリアルインターフェース部

| 項目                   |                   | 記号                             | Min. | Max.               | 単位              | 備考 |

|----------------------|-------------------|--------------------------------|------|--------------------|-----------------|----|

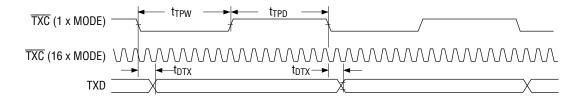

| メインクロック周期            |                   | t <sub>CY</sub>                | 160  | -                  | ns              | 注3 |

| クロック低レベル時間           | $t_{\varphi}^{-}$ | 50                             | -    | ns                 |                 |    |

| クロック高レベル時間           |                   | tφ                             | 70   | t <sub>CY-50</sub> | ns              |    |

| クロック立上り、立下り時間        |                   | t <sub>r</sub> ,t <sub>f</sub> | -    | 20                 | ns              |    |

| TXC<br>の立下りからTXDの遅延時 | <br>間             | t <sub>DTX</sub>               | -    | 1                  | μS              |    |

|                      | 1 x Baud          | f <sub>TX</sub>                | DC   | 64                 | kHz             |    |

| 送信クロック周波数            | 16 × Baud         | t <sub>TX</sub>                | DC   | 615                | kHz             | 注3 |

|                      | 64 × Baud         | t <sub>TX</sub>                | DC   | 615                | kHz             |    |

| 送信クロック低レベル時間         | 1 x Baud          | t <sub>TPW</sub>               | 13   | -                  | t <sub>CY</sub> |    |

|                      | 16 × ,64 × Baud   | t <sub>TPW</sub>               | 2    | -                  | t <sub>CY</sub> |    |

| 送信クロック高レベル時間         | 1 × Baud          | t <sub>TPD</sub>               | 15   | -                  | t <sub>CY</sub> |    |

|                      | 16 × ,64 × Baud   | t <sub>TPD</sub>               | 3    | -                  | t <sub>CY</sub> |    |

|                      | 1 × Baud          | f <sub>RX</sub>                | DC   | 64                 | kHz             |    |

| 受信クロック周波数            | 16 x Baud         | t <sub>RX</sub>                | DC   | 615                | kHz             | 注3 |

|                      | 64 x Baud         | t <sub>RX</sub>                | DC   | 615                | kHz             |    |

| 受信クロック低レベル時間         | 1 × Baud          | t <sub>RPW</sub>               | 13   | -                  | t <sub>CY</sub> |    |

| メロンロンノIMアーハル时日       | 16 × ,64 × Baud   | t <sub>RPW</sub>               | 2    | -                  | t <sub>CY</sub> |    |

| 受信クロック高レベル時間         | 1 × Baud          | t <sub>RPD</sub>               | 15   | -                  | t <sub>CY</sub> |    |

|                      | 16 × ,64 × Baud   | t <sub>RPD</sub>               | 3    | -                  | t <sub>CY</sub> |    |

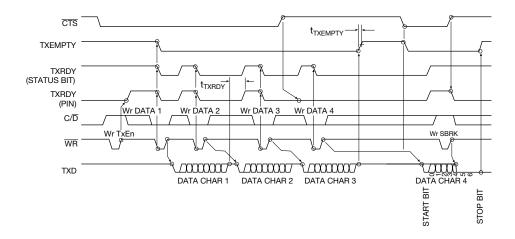

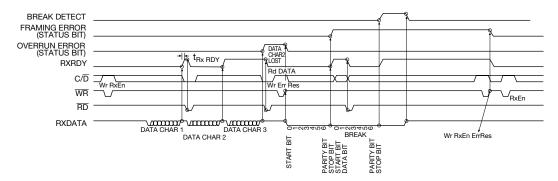

| 項目                              | 記号                          | Min. | Max. | 単位              | 備考 |

|---------------------------------|-----------------------------|------|------|-----------------|----|

| 最終ビットのセンターからTXRDYの立上りまでの時間      | t <sub>TXRDY</sub>          | -    | 8    | t <sub>CY</sub> |    |

| WRの立下りからTXRDYの立下りまでの時間          | t <sub>TXRDY</sub><br>CLEAR | -    | 400  | ns              |    |

| 最終ビットのセンターからRXRDYの立上りまでの時間      | t <sub>RXRDY</sub>          | -    | 26   | t <sub>CY</sub> |    |

| RDの立下りからTXRDYの立下りまでの時間          | t <sub>RXRDY</sub><br>CLEAR | -    | 400  | ns              |    |

| RXCの立上りから内部SYNDETの遅延時間          | t <sub>IS</sub>             | -    | 26   | tcY             |    |

| RXCの立上りに対するSYNDETのセットアップ時間      | t <sub>ES</sub>             | 18   | -    | t <sub>CY</sub> |    |

| 最終ビットのセンターからTXEの遅延時間            | t <sub>TXEMPTY</sub>        | 20   | -    | t <sub>CY</sub> |    |

| WRの立上りからモデム制御信号の遅延時間            | t <sub>WC</sub>             | 8    | -    | t <sub>CY</sub> |    |

| RDの立下りに対するモデム制御信号のセットアップ時間      | t <sub>CR</sub>             | 20   | -    | t <sub>CY</sub> |    |

| RXCの立上りに対するRXDのセットアップ時間(1×Baud) | t <sub>RXDS</sub>           | 11   | -    | t <sub>CY</sub> |    |

| RXCの立上りに対するRXDのホールド時間(1×Baud)   | t <sub>RXDH</sub>           | 17   | -    | t <sub>CY</sub> |    |

注記1: 交流特性は、出力負荷として150pFの容量負荷を接続し、出力は

V<sub>OL</sub> = 0.8V、V<sub>OH</sub> = 2.2V、入力は1.5Vで測定。

注記2: アドレスとは、 CSとC / D

注記3:  $f_{TX}$  or  $f_{RX}$  1 / (30  $t_{CY}$ ) 1 x Baud

$f_{TX}$  or  $f_{RX}$  1/(5 $t_{CY}$ ) 16 x, 64 x Baud

注記4: ステータスワードの更新はステータスに影響を与える事象が発生した後最大28 t<sub>CY</sub>必要とし

ます。

## ■ タイムミング図

#### SYSTEM CLOCK INPUT

#### TRANSMITTER CLOCK AND DATA

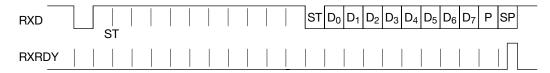

#### • RECEIVER CLOCK AND DATA

#### ■ WRITE DATA CYCLE ( CPU → USART )

#### ● RAED DATA CYCLE (CPU ← USART)

#### • WRITE CONTROL OR OUTPUT PORT CYCLE (CPU → USART)

## ● READ CONTROL OR INPUT PORT (CPU ← USART)

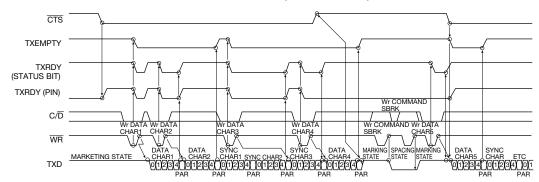

#### • TRANSMITTER CONTROL AND FLAG TIMING ( ASYNC MODE )

注記: 波形図は、7データビット長+パリティビット+2ストップビットの場合です。

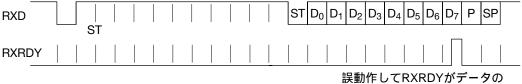

#### RECEIVE CONTROL AND FLAG TIMING (ASYNC MODE)

注記: 波形図は、7データビット長+パリティビット+2ストップビットの場合です。

#### TRANSMITTER CONTROL AND FLAG TIMING (SYNC MODE)

注記: 波形図は、5データビット長 + パリティビットで同期キャラクターが2キャラクターの場合です。

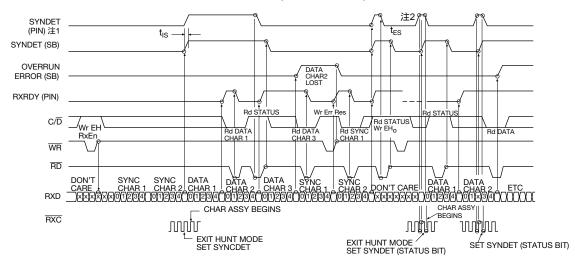

#### • RECEIVER CONTROL AND FLAG TIMING (SYNC MODE)

注記1: 内部同期 5データビット長 + パリティビットで同期キャラクターが2キャラクターの場合です。

注記2: 外部同期 5データビット長+パリティビットの場合です。

# ■ 端子説明

| 端子名                             | 入力<br>出力 | 機能説明                                                                                                                                                                                                                                                                                                                                |

|---------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>0</sub> ~ D <sub>7</sub> | 入出力      | 双方向のデータバスで、コントロールワード、ステータスワード、データをCPU に対し入出力します。                                                                                                                                                                                                                                                                                    |

| RESET                           | 入力       | RESET端子にHighレベルを印加すると82C51A-2は、RESET状態となり、モード命令の書き込み待ち状態となります。<br>最小RESET幅はCLK(MAIN CLOCK)が動作状態で6クロック分です。                                                                                                                                                                                                                           |

| CLK                             | 入力       | CLK信号は、内部タイミングを作成するために使用されます。<br>CLK信号とRXC、TXCとは非同期で動作しますが、同期及びX1Band(非同期)では、RXC、TXCの30倍以上、×16、×64Baud(非同期)では、RXC、TXCの5倍以上の周波数でなければなりません。                                                                                                                                                                                           |

| WR                              | 入力       | アクティブLowの入力端子で、CPUから送信データやコントロールワードを82C51A-2に書き込む信号です。                                                                                                                                                                                                                                                                              |

| RD                              | 入力       | アクティブLowの入力端子で、82C51A-2から受信データやステータスワードを読み出す信号です。                                                                                                                                                                                                                                                                                   |

| C/D                             | 入力       | CPUから82C51A-2をアクセスする時にデータorコマンドワード、ステータスワードかを選択する信号です。 C/ $\overline{D}$ =Lowの場合には、転送データー C/ $\overline{D}$ =Highの場合には、コマンドワード又はステータスワードをアクセスします。                                                                                                                                                                                   |

| <u>CS</u>                       | 入力       | アクティブ、Lowの入力端子で、CPUが82C51A-Sをアクセスする時に、Lowとし、<br>デバイスをセレクトします。<br>注)CS = Highの状態だけでは、待機状態となりません。<br>待機状態に関する説明を参照。                                                                                                                                                                                                                   |

| TXD                             | 出力       | 送信データー出力端子で、シリアルに変換されたデーターが出力されます。<br>RESET後や送信停止状態ではマーク状態(Highレベル)となっています。<br>又、コマンド命令により、ブレーク状態(Lowレベル)に設定する事もできます。<br>リセットによりHighレベルとなります。                                                                                                                                                                                       |

| TXRDY                           | 出力       | TXRDY端子は、送信データーキャラクターを受付け可能である事を示す出力端子です。ただし、CTS=High又はコマンド命令によりTX Disable状態に設定した時は常に、TXRDY=Lowとなります。 注)ステータスワードのTXRDYは、CTSやコマンド命令に無関係に、送信データーキャラクターが受付け可能であるかを示します。 TXRDYはCPUがデータキャラクターを書き込むとWR信号の前縁によりリセットされます。リセットによりLowレベルとなります。                                                                                                |

| TXEMPTY                         | 出力       | TXEMPTY端子は82C51A-2が送信するキャラクターが無くなった時にHighとなります。 同期モードでは、送信データーキャラクターが無くなり、同期キャラクターが自動送信されていても、データーキャラクターを書き込まない限りHighとなります。 TXEMPTYは、CPUがデータキャラクターを書き込むとWR信号の前縁によりリセットされます。 CTS= " High " 又はコマンドで送信停止をすると、それ以前に書き込んだデータを送出後TXD= " High "、TXEMPTY= " High " となります。 CTS又はコマンドで送信停止後にデーターを書き込んだ場合でも同様です。(タイミング図参照)リセットによりHighレベルになります。 |

| 端子名           | 入力<br>出力 | 機能説明                                                                                                                                                                                                                                                                                       |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXC           | 入力       | TXCは送信データーの転送スピードを決めるクロック入力信号です。<br>同期モードでは、ボーレートはTXCの周波数と同じとなります。<br>非同期モードでは、モード命令により、ボーレートをTXCの1倍、1/16倍、1/64倍の中から選択できます。<br>送信データーは、TXCの立下りエッジに同期して、TXDより出力します。                                                                                                                         |

| RXD           | 入力       | RXDは、シリアルデーターを受信する入力端子です。                                                                                                                                                                                                                                                                  |

| RXRDY         | 出力       | RXRDY端子は、受信を完了したキャラクターが82C51A内部に有る事を示す出力端子です。 RXRDYはCPUがデーターキャラクターを読み出すと、RD信号の前縁によりリセットされます。 RXRDYがHighとなった後、次の1キャラクター受信終了前に読み出さないと、前のデーターは失われます。その場合には、ステータスワードのオーバーランエラーフラグがセットされます。 リセットによりLowレベルとなります。                                                                                 |

| RXC           | 入力       | RXCは受信データーの転送スピードを決めるクロック入力信号です。<br>同期モードでは、ボーレートはRXCの周波数と同じとなります。<br>非同期モードでは、モード命令により、ボーレートをRXCの1倍、1/16倍、1/64倍の中から選択できます。<br>受信データーは、RXCの立上りエッジでサンプリングします。                                                                                                                               |

| SYNDET<br>/BD | 入力出力     | SYNDET/BDはモードにより機能が変わる端子です。 内部同期モードでは、同期キャラクターを受信して、キャラクター同期が取れるとHighとなる出力端子です。ステータスワードを読み出すと、リセットされます。外部同期モードでは、外部からの同期信号を入力する入力端子となります。この場合には、外部信号によりデーター受信を開始します。非同期モードでは、出力端子となり、受信データーが連続した2キャラクター分に相当する期間連続してLowであると、ブレークキャラクターを検出したとして、この端子にHighが出力されます。この端子は、RXDがHighになるとリセットされます。 |

| DSR           | 入力       | モデムインターフェース用の入力ポードです。端子の入力状態は、ステータスワードで読む事でCPUは認識できます。                                                                                                                                                                                                                                     |

| DTR           | 出力       | モデムインターフェース用の出力ポードです。コマンド命令により、DTRの状態を設定する事ができます。リセットによりHighレベルとなります。                                                                                                                                                                                                                      |

| CTS           | 入力       | モデムインターフェース用の入力端子で、送信回路の制御に使用します。コマンド命令でTX Enableとしますと、CTSで送信を制御できます。CTS = Lowで送信可となります。                                                                                                                                                                                                   |

| RTS           | 出力       | モデムインターフェース用の出力用ポードです。コマンド命令によりRTSの状態を設定する事ができます。リセットによりHighレベルになります。                                                                                                                                                                                                                      |

#### ■ 機能

#### ●概要

MSM82C51A-2は、マイクロプロセッサーの周辺デバイスとして、CPUとの間で機能の設定、コマンドの設定、ステータスの読み出し、データーの入出力等をプログラムで行います。 CPUと82C51A-2の間のオペレーションを表1に示します。

| CS | C/D | RD | WR |                  |

|----|-----|----|----|------------------|

| 1  | ×   | ×  | ×  | データーバス 3 - State |

| 0  | ×   | 1  | 1  | データーバス 3 - State |

| 0  | 1   | 0  | 1  | ステータス → CPU      |

| 0  | 1   | 1  | 0  | コントロールワード ← CPU  |

| 0  | 0   | 0  | 1  | データー → CPU       |

| 0  | 0   | 1  | 0  | データー ← CPU       |

表1. 82C51A-2とCPU間のオペレーション

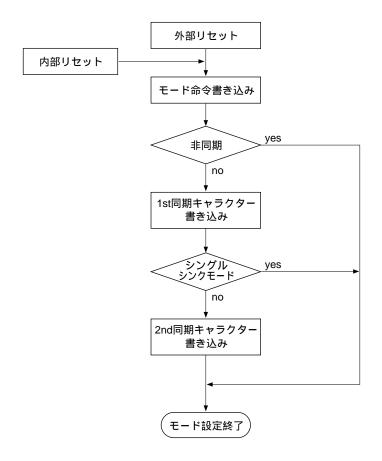

82C51A-2はRESET後に機能設定シーケンスを実行する必要が有ります。機能設定シーケンスを図1に示します。

機能設定が終了すると、コマンド命令受け入れ状態となり、必要なコマンド設定、ステータスの読み出し、データーのREAD/WRITEにより、データーの転送ができます。

図1 機能設定シーケンス(モード命令シーケンス)

#### ●コントロールワード

コントロールワードには、2つの形式が有ります。

- 1. モード命令(機能設定)

- 2. コマンド命令(動作設定)

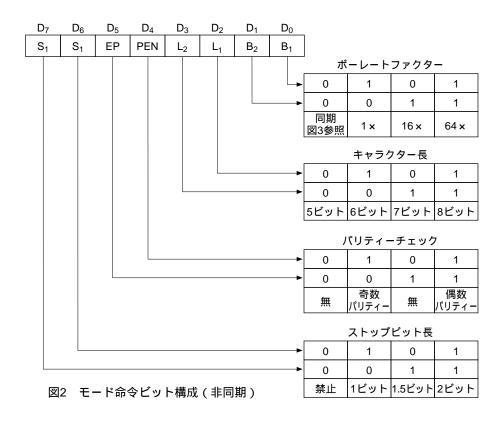

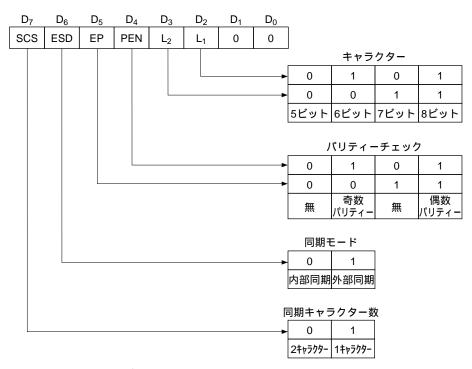

#### (1) モード命令

モード命令は82C51A-2の機能の設定に用います。

内部リセットまたは外部リセットにより、モード命令の書き込み待ちとなります。すなわち、 リセット後のコントロールワードの書き込みは、モード命令と認識されます。モード命令で設 定する項目は、以下の通りです。

- ・同期/非同期モード

- ・ストップビット長(非同期モード)

- ・キャラクター長

- ・パリティービット

- ・ボーレートファクター(非同期モード)

- ・内部 / 外部同期 (同期モード)

- ・同期キャラクター数(同期モード)

モード命令のビット構成は、図2、3に示します。更に、同期モードの場合には、1 or 2byteの同期キャラクターを書き込む必要があります。同期キャラクターの書き込みも、モード命令の一部となりますので、同期キャラクターの書き込みが終ると、機能の設定が完了します。

図3 モード命令ビット構成(同期)

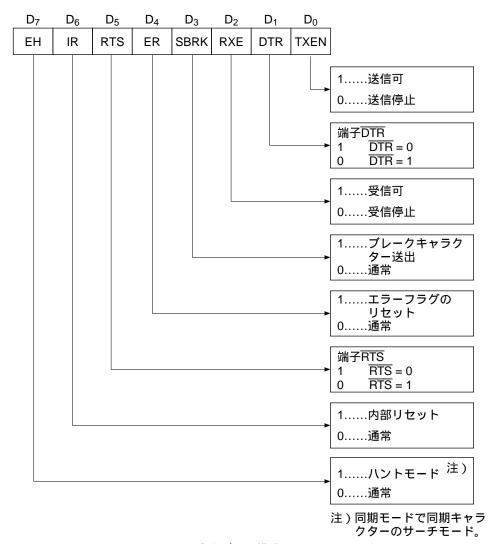

#### (2)コマンド命令

コマンド命令は、82C51A-2の動作の設定に用います。

コマンド命令は、モード命令、同期キャラクターを書き込んだ後、必要な時に書き込むことが できます。

コマンド命令で設定する項目は、以下の通りです。

- ・送信Enable/Disable

- ・受信Enable/Disable

- ・DTR、RTS端子へのデーター出力

- ・エラーフラグのリセット

- ・ブレークキャラクターの送出

- ・内部リセット

- ・ハントモード(同期モード)

コマンド命令のビット構成は、図4に示します。

図4 コマンド命令ビット構成

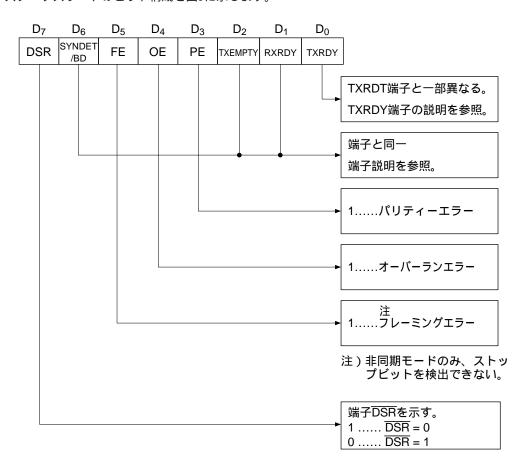

#### ●ステータスワード

82C51A-2の内部状態は、ステータスワードを読み出す事で見る事ができます。 ステータスワードのビット構成を図5に示します。

図5 ステータスワードビット構成

#### ● 待機状態

MSM82C51A-2は、CMOS・完全スタティック構成のため、待機状態にする事が可能です。 MSM82C51A-2の待機状態は下記の条件を満足した時です。

- ① CS端子はV<sub>CC</sub>電位に設定。

- ② CS、 $D_0 \sim D_7$ 、 $\overline{RD}$ 、 $\overline{WR}$ 、C /  $\overline{D}$ を除く入力ピンは、 $V_{CC}$ 電位またはGND電位に設定。 (外部同期モード時は、SYNDETを含む)

注記: 出力端子は出力電流がゼロとなる様に設定されれば待機時電源電流規格を満足します。

#### ●使用上の注意

MSM82C51A/A-2には、下記に示す様な問題点がありますので、使用する上で注意願います。

#### 1. スタートビットのハーフビット処理

82C51Aを非同期モードで使用する場合に、1データービット長に満たないスタートビットに対する処理に問題があります。(図1参照)

| スタートビット長     | モード  | 動作                   |

|--------------|------|----------------------|

| 7受信クロック長以下   | × 16 | 短いスタートビットは無視される。(正常) |

| 31受信クロック長以下  | × 64 | 短いスタートビットは無視される。(正常) |

| 8受信クロック長     | × 16 | 誤動作し、正しくデータを受信できない。  |

| 32受信クロック長    | × 64 | 誤動作し、正しくデータを受信できない。  |

| 9~16受信クロック長  | × 16 | スタートビットと見なす。(正常)     |

| 33~64受信クロック長 | × 64 | スタートビットと見なす。(正常)     |

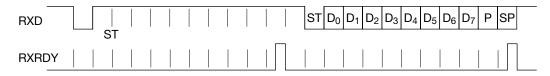

#### 2. ブレーク信号受信後のパリティーフラグ(図2参照)

82C51Aを非同期モードで使用する場合において、ブレーク信号受信後に次の正常データーを読み込むとパリティーフラグがセットされている場合が有ります。

パリティーフラグがセットされる条件は、ブレーク信号の立ち上がり(ブレーク信号の終了)が、最終データービットから、パリティービットまでの近辺で変化する場合に、パリティーフラグはセットされるが、RXRDY信号が出力されない場合が有ります。

このため、そのような場合には、次の正常なデーター受信時にもパリティーフラグがセットされたままのため、受信データーがパリティーエラーの様に見えます。

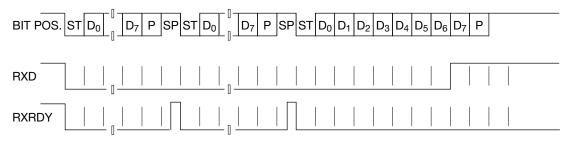

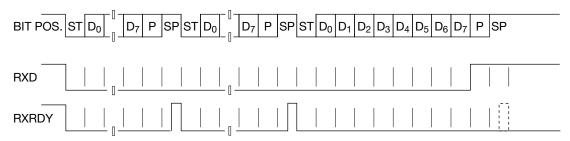

#### 3. ブレークディテクト (BD) 信号によるRXD信号マーク処理 (図3参照)

RXDブレーク時にBD信号によって外部回路にてRXDをマーク (High) 状態にするとフレーミングエラーはセットされるが、RXRDYが発生しない場合があります。このため次に正常なデータを受信したときにもフレーミングエラーがセットされたままであるため、受信データにフレーミングエラーがあるように見えます。

BDが立ち上がって更にRXRDYが立ち上がったことを確認してRXDを立ち上げるような外部回路にするようにしてください。

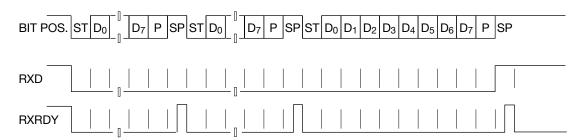

# 〔図1〕スタートビットのハーフビット処理タイミング図

#### ●通常動作時

| RXD   | STD | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | Р | ST | ST | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | Р | SP |  |

|-------|-----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|----|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|----|--|

| RXRDY |     |                |                |                |                |                |                |                |   |    |    |                |                |                |                |                |                |                |                |   |    |  |

#### ●スタートビットが1/2データビットより短い場合

## ●スタートビットが1/2データビットの場合(82C51Aの問題点)

受信途中に出力される

## ● スタートビットが1 / 2データビットを越える場合

ST : スタートビット : ストップビット SP Р : パリティービット  $D_0 \sim D_7$ : データビット

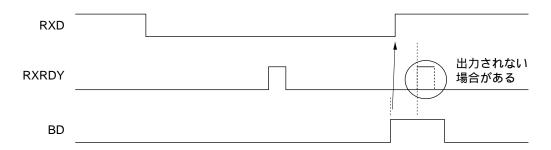

# [図2] ブレーク信号受信タイミングとパリティフラグ

# ●正常動作

パリティーフラグはセットされない RXRDYも出ない

# ●問題のタイミング

パリティーフラグはセットされるが RXRDYは出ない

## ●正常動作

パリティーフラグはセットされる RXRDYは出力される

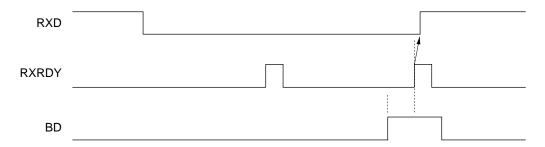

# 〔図3〕

●問題となるタイミング(BDによりRXDを立ち上げる場合)

●正常動作(BD and RXRDYでRXDを立ち上げる場合)

# ■ 付録

# ● 低速版から高速版への置き換え時の注意事項

従来生産しておりました低速版は、下記表のとおり高速版に集約されております。低速版をお使いの 方で高速版に置き換えをされる方は、次ページ以降の置き換え時の注意事項をお読みください。

| 古法以制口夕(佳奶制口) | (1) 本版制 口名 ( 南口 ) | 備考          |

|--------------|-------------------|-------------|

| 高速版製品名(集約製品) | 低速版製品名(廃品)        | 1佣1号        |

| M80C85AH     | M80C85A/M80C85A-2 | 8bit MPU    |

| M80C86A-10   | M80C86A/M80C86A-2 | 16bit MPU   |

| M80C88A-10   | M80C88A/M80C88A-2 | 8bit MPU    |

| M82C84A-2    | M82C84A/M82C84A-5 | クロックジェネレータ  |

| M81C55-5     | M81C55            | RAM,I/O,タイマ |

| M82C37B-5    | M82C37A/M82C37A-5 | DMAコントローラ   |

| M82C51A-2    | M82C51A           | USART       |

| M82C53-2     | M82C53-5          | タイマ         |

| M82C55A-2    | M82C55A-5         | PPI         |

#### MSM82C51AとMSM82C51A-2との相違点

#### 1) 製造プロセスの相違点

どちらも $3\mu$ Si-Gate CMOSプロセスであり相違点はありません。また、チップサイズも同じです。

#### 2)機能上の相違点

下記3-2)項のAC特性が変更になっているのみで論理の相違はありません。

#### 3)規格上の相違点

#### 3-1) DC特性

| 項目      | 記号  | MSM82C51A | MSM82C51A-2 |

|---------|-----|-----------|-------------|

| VoL測定条件 | loL | + 2.0 mA  | + 2.5 mA    |

| VOH測定条件 | Іон | 400 μΑ    | 2.5 mA      |

上記のとおり出力電圧の規格自体は同じであるが、MSM82C51A-2の条件はMSM82C51Aより厳しい条件になっているため問題はありません。

#### 3-2) AC特性

| 項目                         | 記号  | MSM82C51A                | MSM82C51A-2             |

|----------------------------|-----|--------------------------|-------------------------|

| RDパルス幅                     | trr | 250 ns 最小                | 130 ns 最小               |

| RDの立ち下りから<br>データ確定時間       | trd | 200 ns 最大                | 100 ns 最大               |

| RDの立ち上りから<br>データフロート時間     | trF | 100 ns 最大                | 75 ns 最小                |

| WRパルス幅                     | tww | 250 ns 最小                | 100 ns 最小               |

| WRの立ち上りに対する<br>データセットアップ時間 | tow | 150 ns 最小                | 100 ns 最小               |

| WRの立ち上りに対する<br>データホールド時間   | two | 20 ns 最小                 | 0 ns 最小                 |

| メインクロック周期                  | tcy | 250 ns 最小                | 160 ns 最小               |

| クロック低レベル時間                 | tφ  | 90 ns 最小                 | 50 ns 最小                |

| クロック高レベル時間                 | tφ  | 120 ns 最小<br>tcy 90 ns最大 | 70 ns 最小<br>tcy 50 ns最大 |

上記のとおりMSM82C51A-2の規格は、MSM82C51Aの規格を満足しているため問題はありません。

以上

## ■ パッケージ寸法図

(単位:mm)

#### 表面実装型パッケージ実装上のご注意

SOP、QFP、TSOP、TQFP、LQFP、SOJ、QFJ(PLCC)、SHP、BGA等は表面実装型パッケージであり、リフロー実装時の熱や保管時のパッケージの吸湿量等に大変影響を受けやすいパッケージです。

したがって、リフロー実装の実施を検討される際には、その製品名、パッケージ名、ピン数、パッケージコード及び希望されている実装条件(リフロー方法、温度、回数)、保管条件などを弊社担当営業まで必ずお問い合わせください。